International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 3, Issue 1, March 2023

# Design of Low Power Low Offset Dynamic latch Comparator using DTMOS Technique

Hemalatha B<sup>1</sup>, Dr. Ajay Kumar Dadoria<sup>2</sup>, J Aparna Priya<sup>3</sup>

Research Scholar<sup>1,3</sup> and Assistant Professor<sup>2</sup> Amity University, Gwalior, M.P. India

**Abstract:** Analog to Digital converters plays an essential role in signal processing and medical applications. SAR ADC is best suited for biomedical applications because of its low power and medium resolution. Low power dynamic comparators are essentially desired in the design of SAR ADC. In this paper, a lowpower dynamic type latch comparator is designed which is based on Dynamic Threshold Metal Oxide Semiconductor (DTMOS) technique to reduce the power dissipation which is achieved by reducing the supply voltage. The circuit has been implemented at the supply voltage of 0.8 V. The simulations for this comparator are carried out in CADENCE SPECTRE using 45nm CMOS technology. The simulation outcomes validate that the designed dynamic latch comparator with DTMOS techniques is 20% morepower saving in comparison to the conventional comparator. The total power consumption is as low as 156.18nW which makes it suitable for low-power bio-medical applications.

Keywords: Dynamic latch comparator, Low power, SAR- ADC, DTMOS..

### I. INTRODUCTION

The vital demand of low-power mixed mode devices like Analog to digital converters (ADCs) [15] has enforced the design of low power [24], [17]. Various portable and small feature sized electronic devices which are used in medical systems require ADCs with low power and fast switchingspeed [20]. The dominant block of ADC is comparator, which determines the overall performance of ADC. So as to enhance the battery life and accuracy of ADC, the comparator must be of high speed and energy efficient. The comparator predominantly incorporates two stages, firstone is a reset stage and the second one is a comparing stage. The one of most eminent standard for deducting power consumption is to scale down the input voltage supply, since in CMOS circuits average power consumption is square of the input supply voltage.

$P = Vdd^2 I_d$

As the CMOS technology is down scaling, the problem of low voltage has occurred in case of low power -high speed comparators, because the threshold voltage is not scaled with respect to the supply voltage [24]. This constrains the voltage head room [25] as well as Input Common Mode Range (ICMR). Also, the offset of CMOS devices which is caused by the mismatches in capacitance and current factor, approx- imately doubles for every process variation below 100nm CMOS technology [9]. Thus it has become a major challenge to design a high speed low-power comparator in the design of ADC.

Comparators with various design techniques have been proposed to meet the accuracy and the overall performance requirements of ADCs [22]. The various techniques are as such fully differential approach [22], body driven technique [26]- [16], offset cancellation technique [7]- [12], zero thresh- old voltage MOS based technique [21] and supply voltage boosting method [11] etc. These techniques are absolutely satisfactory but not supportive for low supply voltage at Ultra Deep Submicron (UDSM) CMOS technology. These drawbacks of low power consumption are overcome by design the comparator circuit with DTMOS technique.

When compared to the static type comparators, dynamic comparators exploits dynamic bias and positive feedback, because of which they provide low static power consumption [11]

Copyright to IJARSCT www.ijarsct.co.in DOI: 10.48175/IJARSCT-8951G

International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 3, Issue 1, March 2023

### **II. DTMOS TECHNIQUE**

In the recent days the size of the transistor is reducing, because of this reduced size of MOS transistor, it demands the lower supply voltage [10]. In fields of biomedical devices like EEG, ECG, EMG portable monitoring systems requires minimum sized batteries, therefore low voltage low power circuits are required. This can be achieved by reducing the supply voltage, but this will effectively degrade the signal quality, output resistance of MOS transistor and voltage gain. Hence So LVLP (Low Voltage Low Power) techniques have been developed in CMOS technology [2], [19], [5], [13], [8]. One of the LVLP term is DTMOS (Dynamic Threshold MOS) transistor. DTMOS was first suggested by [4], [23]. DTMOS transistor have the ability to dynamically regulate the threshold voltage ( $V_{th}$ ) of transistor, using body biasing technique.

In DTMOS technique, threshold voltage can be reduced by connecting together the gate of the MOS transistor to its body. This meaningfully enhances the current drive of the DTMOS [1], [18].

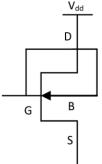

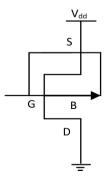

Figures 1 ans 2. show the DTMOS structures for NMOS and PMOS transistors. When DTMOS transistor is in conduction (ON), its threshold voltage (Vt) decreases and driving current increases, propagation delay decreases. On the other hand, if a DTMOS transistor is not conducting (OFF), then the threshold voltage increases, leakage current decreases and thus power consumption also decreases. In this paper, a dynamic latch comparator is designed with DTMOS technique and compared it with the conventional dynamic latch comparator. The design is simulated using 45 nm CMOS technology.

Fig. 1. n-MOSFET structure of DTMOS

Fig. 2. p- MOSFET structure of DTMOS

#### III. EXISTING DESIGN OF DYNAMIC LATCH COMPARATOR CIRCUIT DESCRIPTION

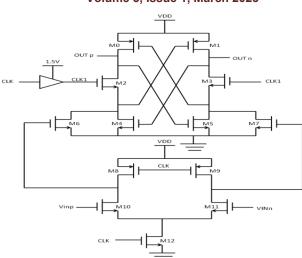

The schematic diagram of conventional dynamic latch type comparator is illustrated in Fig.3, where the comparator is designed and simulted in 180nm CMOS technology. CLK1 is the level shifted signal of CLK with a delay of nearly 90ps. This comparator operates in two phases. In reset phase i.e., when clock is LOW, the transistors M6, M7, M0, M1 and VDD are ON, and M2 and M3 are OFF. The input nodes are discharge to ground via transistors M6 and M7, and nodesOUTp AND OUTn are charged to VDD via transistor M0 andM1.

Copyright to IJARSCT www.ijarsct.co.in DOI: 10.48175/IJARSCT-8951G

International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 3, Issue 1, March 2023

Fig. 3. Schematic of conventional Dynamic Latch Comparator (DLC)

When the clock goes HIGH, the reset transistors are switched OFF and the currents starts flowing in M12 as well as in the differential pair. Based on the input voltage, one of the cross-coupled inverters M0, M1, M4, M5, that makes the regeneration, receives large current, which determines the final output state. when regeneration is finished, one of the output node is at VDD; the next output and both the drains of the differential pair have a 0-V potential. In this context, there is no supply current and hence power efficiency is maximized.

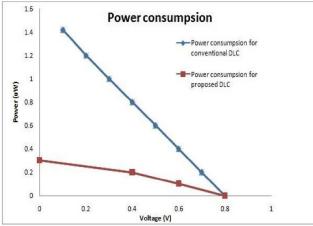

While the drain voltage of any one of the transistors falls below VDD- IVth I, NMOS transitor of the inverter will turn ON and output node will start to discharge ; positive feedback is turned ON. When the output reaches VDD- IVth I PMOS transistor of another inverter will turn ON. Consequently output is regenerated and after the regeneration phase one of the output is logic '0' and the other is logic '1'. Fig.4 shows that power consumption of the conventional circuit is  $39.516\mu$ W.

Fig. 4. Power consumption of conventional Dynamic Latch Comparator

### IV. PROPOSED DESIGN OF DTMOS DYNAMIC LATCH COMPARATOR

#### 4.1 Circuit Description

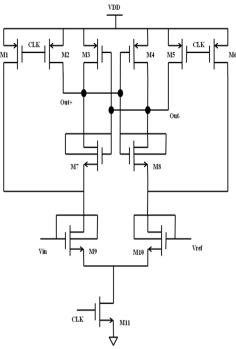

Fig. 5 Shows the design of proposed dynamic latch com- parator using dynamic threshold MOS transistor logic. The circuit is redesigned at 45nm CMOS technology. The main objective of redesigning the circuit at 45nm CMOS process this circuit is to reduce the power consumption. So the technique of DTMOS which is a low power technique is utilized in implementing a low power dynamic latch comparator. The proposed dynamic comparator also operates like a conventional circuit at two stages. In first stage i.e. when the clock is logic '0' the transistors of M1/M6 and M2/M5 are

Copyright to IJARSCT www.ijarsct.co.in DOI: 10.48175/IJARSCT-8951G

International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 3, Issue 1, March 2023

reset the output node and drain of the various transistors M9/M10 are connected to VDD. The tail transistor M11 is OFF and no supply current remains. When the clock logic '1' the reset transistors are turned OFF and the flows begins streaming in M11 as well as in the differential pair. In view of the input voltage, one of the cross- coupled inverters M7/M3 or M8/M4 that makes the recovery, gets huge current, which decides the last output state. at thepoint when recovery is done, one of the output node is at VDD; the following output and both the channels of the differential pair have a 0-V potential. In this unique situation, there is no stockpile current and henceforth power effectiveness is expanded. While the channel voltage of any of the transistors falls underneath VDD-|Vth|, NMOS transistor of the inverter will turn ON and output node will begin to release ; positive input is turned ON. At the point when the output arrives at VDD-|Vth| PMOS transistor of another inverter will turn ON. Subsequently output is recovered and after the recovery stage one of the output is rationale '0' and the other is rationale '1'. In this process the supply voltage is divided at the transistors of M7/M8 and M9/M10 here the half of the supply voltage will be flowing and that design operates in that supply voltage

Fig. 4. Schematic diagram of proposed DTMOS- Dynamic Latch Comparator TABLE.1 TRANSISTOR ASPECT RATIOS IN THE PROPOSED DYNAMIC LATCHCOMPARATOR

| Transistor ID | Aspect Ratios (µm) |  |

|---------------|--------------------|--|

| M1,2          | 18/0.26            |  |

| M3,4          | 0.9/0.26           |  |

| M5,6          | 0.45/0.26          |  |

| M7,8,9,10     | 0.9/0.26           |  |

| M11           | 0.45/0.26          |  |

Potential dividing theorem is used to find the values of R1 and R2. The technique of DTMOS is applied in NMOS and PMOS pairs to reduce the total power consumption.

Applying potential dividing concept in NMOS and PMOS pairs, dynamic threshold voltage is determined.

V x R2/ R1 + R2

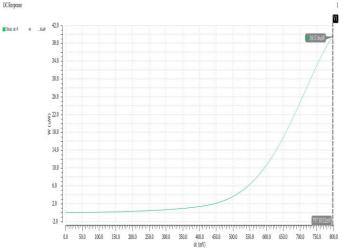

From the DC response of the proposed circuit we can state that power consumption is reduced to 156.18nW of power consumption reduced by employing the DTMOS technique.

Copyright to IJARSCT www.ijarsct.co.in DOI: 10.48175/IJARSCT-8951G

International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 3, Issue 1, March 2023

#### V. SIMULATION RESULTS AND DISCUSSION

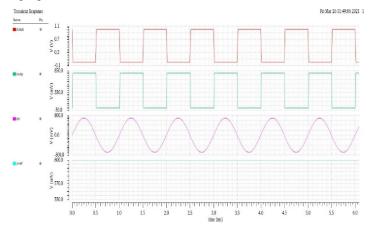

The proposed dynamic latch comparator with Dynamic Threshold MOS (DTMOS) is compared with the existing dynamic latch comparator using SPECTRE simulator in CADENCE at 45nm CMOS process at VDD = 0.8 V. The same simulation environment is used to make a fair comparison.

Figures below depict the comparison of power dissipation of existing and proposed comparator circuits. Fig. 5 shows the transient response of the proposed circuit

Fig.5. Transient response of dynamic latch comparator

Fig. 6. Power consumption versus voltage of proposed DTMOS and Conventional Dynamic Latch Comparator Fig. 6 shows that power dissipation is lower compared to the existing circuit without affecting the performance of the circuit.

DOI: 10.48175/IJARSCT-8951G

Copyright to IJARSCT www.ijarsct.co.in ISSN 2581-9429 IJARSCT

International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 3, Issue 1, March 2023

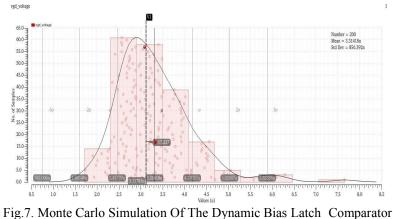

Fig. 7 shows the standard deviation of the offset of the proposed comparator, that is 856.392nV using Monte Carlo Simulations for a run of 200 samples. Based on the simulation results, Table-I presents the comparison between the proposed and other two dynamic comparators.

TABLE-II PERFORMANCE COMPARISON OF PROPOSED COMPARATOR WITH AN EXISTING

| COMPARATOR        |        |          |          |  |  |

|-------------------|--------|----------|----------|--|--|

| Parameters        | [1]    | [2]      | Proposed |  |  |

| CMOS Technology   | 180nm  | 45nm     | 45nm     |  |  |

| Supply voltage    | 1.8V   | 0.8V     | 0.8V     |  |  |

| Power consumption | 72.2µW | 39.516µW | 156.18nW |  |  |

| Delay             | 268ps  | -        | 105.6µs  |  |  |

# VI. CONCLUSION

A low power dynamic latch comparator design is presented in this paper to decline the supply voltage and power consumption. The structure of the existing comparator circuit is modified by applying dynamic threshold MOS technique. The simulation results approve the reduction in input supply voltage and power consumption as well in comparison with the existing comparator. The proposed comparator dissipates very less power of 156.18nW at a supply voltage of 0.8V.

### VII. FUTURE SCOPE

The proposed dynamic latch comparator was designed with the objective of decreasing the power. A low power technique called a Dynamic Threshold MOS (DTMOS) technique is implemented in the design of the dynamic latch comparator. The proposed comparator achieves the lowest power consumption of 156.18nW. However, the delay could not be decreased than that of the reference comparators. This circuitcan be further modified to reduce the delay

### REFERENCES

- [1]. Allen, P.E., and Holberg, D.R., "CMOS analog circuit design", Oxford: Oxford University Press, 2002.

- [2]. B. Goll and H.Zimmerman, "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65," IEEE Trans Circuits Syst.II, Exp Briefs, Vol. 56, no.11, pp. 810-814, Nov. 2009.

- [3]. Witch, B. Nirschl, T. and Schmitt-Landsiedel, D., "Yield and speed optimization of a latch-type voltage sense amplifier", IEEE Journal of Solid State Circuits, Vol. 39, no.7, pp. 1148-1158, 2004.

- [4]. Ragab, K., Chen, L., Sanyal, A., and Sun, N., "Digital background calibration for pipelined ADCs based on comparator decision time quantization ", IEEE Trans Circuits Syst.II, Exp Briefs, Vol. 62, no.5, pp. 456-460, 2015.

- [5]. Goll, B., and Zimmermann, H., "A 65nm CMOS comparator with modified latch to achieve 7GHz/1.3W at

- [6]. 1.2 V and 700MHz/47 IW at 0.6 V", IEEE International Solid-State Circuits Conference (ISSCC) Digest Technical Papers, pp. 328–329, 2009.

- [7]. Kim, Jaeha, Kevin D. Jones, and Mark A. Horowitz, "Fast, non-monte carlo estimation of transient performance variation due to device mismatch", IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 7, pp. 1746-1755, 2010.

- [8]. Katyal, V., Geiger, R. L., and Chen, D. J., "A new high precision low offset dynamic comparator for high resolution high speed ADCs", In IEEE Asia Pacific Conference on Circuits and Systems, pp. 5-8, 2006.

- [9]. Maymandi-Nejad, M., and Sachdev, M., "1-bit quantizer with rail to rail input range for sub-1 V Σ-Δ modulators", Electronics Letters, vol. 39, pp. 894–895, 2003.

- [10]. Lu, J. and Holleman, J., "A low-power high-precision comparator withtime-domain bulk-tuned offset cancellation", IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 60, pp. 1158-1167, 2013.

- [11]. Dubey, Avaneesh K., and R. K. Nagaria, "Enhanced Gain Low-Power CMOS Amplifiers: A Novel Design Approach Using Bulk-Driven Load and Introduction to GACOBA Technique," Journal of Circuits, Systems and Computers (JCSC), vol. 27, no. 13, 2018.

DOI: 10.48175/IJARSCT-8951G

International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 3, Issue 1, March 2023

- [12]. Hassanpourghadi, M., Zamani, M., and Sharifkhani, M., "A low-power low-offset dynamic comparator for analog to digital converters", Microelectronics Journal, vol. 45, pp. 256-262, 2014.

- [13]. Chiang, S. H. W., "Comparator offset calibration using unbalanced clocks for high speed and high power efficiency", Electronics Letters, vol. 52, pp. 1206-1207, 2016.

- [14]. Dubey, Avaneesh K., and R. K. Nagaria, "Optimization for offset and kickback-noise in novel CMOS double-tail dynamic comparator: A lowpower, high-speed design approach using bulk-driven load," Microelectronics Journal, vol. 78, pp. 1-10, 2018.

- [15]. Kandala, M., and Wang, H., "A 0.5 V high-speed comparator with railto-rail input range", Analog Integrated Circuits and Signal Processing, vol. 73, pp. 415-421, 2012.

- [16]. Mesgarani, A., Alam, M. N., Nelson, F. Z., and Ay, S. U., "Supply boosting technique for designing very low-voltage mixed signal circuits in standard CMOS", In 53rd IEEE international midwest symposium on circuits and systems, pp. 893–896, 2010.

- [17]. T.B Cho and P.R. Gray, "A 10b, 20 Msamples/s, 35mW pipeline A/D converter," IEEEJ.Solid -State Circuits, Vol.30, no.3, pp.166-172, Mar.1995.

- [18]. Khateb, F., Dabbous, S.B.A., Vlassis, S.: A survey of non- conventional techniques or low-voltage low-power analog circuit design. Radioengineering 22, 415–427, 2013.

- [19]. Yan, S., Sanchez-Sinencio, E.: Low voltage analog circuit design techniques: a tutorial.IEICE Trans. Analog Integr. Circ. Syst. E00-A(2), 2000.

- [20]. Khateb, F., Khatib, N., Koton, J.: Novel low-voltage ultra- low power DVCC based on floating-gate folded cascade OTA. Microelectron. J. 42, 1010–1017, 2011.

- [21]. Farshidi, E., Keramatzadeh, A.: A new approach for low voltage CMOS based on current-controlled conveyors. IJE Trans. B: Appl. 27, 723–730, 2014.

- [22]. Ramirez-Angulo, J., Lopez-Martin, A.J., Carvajal, R.G., Chavero, F.M.: Very low-volatge analog signal processing based on quasi-floating gate transistors. IEEE J. Solid-State Circ.39, 434–442, 2003.

- [23]. Fallah, M., MiarNaimi, H.: A novel low voltage, low power and high gain operational amplifier using negativeresistance and self cascode transistors. IJE Trans. C: Aspects 26, 303–308, 2013.

- [24]. Assaderaghi, F., Sinitsky, D., Parke, S.A., et al.: Dynamic threshold-voltage MOSFET (DTMOS) for ultralow- voltage VLSI. IEEE Trans. Electron Devices 44, 414–422, 1997.

- [25]. Assaderaghi, F., Parke, S.A., Sinitskyd, D., Bokor, J., Ko, P.K., Hu, C.: Dynamic threshold-voltage MOSFET (DTMOS) for very low-voltage operation. IEEE Device Lett.15, 510–512, 1994.

- [26]. Shieh, M.S., Chen, P.S., Tsai, M.J., Lei, T.F.: A novel dynamic threshold voltage MOSFET (DTMOS) using heterostructure channel of Si1 yCy interlayer. IEEE Electron Device Lett.26, 740–742, 2005.

- [27]. Kang, S.M., Leblebici, Y.: CMOS Digital Integrated Circuit : Analysis and Design. TMH, 2008.