International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 5, Issue 10, June 2025

# Design of An Automated Car Washing System with Verilog HDL

Rishabhsmallir<sup>1</sup>, Sindhus<sup>1</sup>, Dr. Manjulabb<sup>1</sup>, Dr. Sghiremath<sup>1</sup>

Department of Electronics and Communication and Engineering<sup>1</sup> East Point College of Engineering and Technology, Bangalore

Abstract: Automation remains at the forefront of technological innovation, enabling the efficient control of processes without direct human involvement This project presents an advanced automated car washing system utilizing Field Programmable Gate Arrays (FPGAs) programmed in Verilog HDL. The system provides washing services that are rapid, convenient, and effective. A flow chart for controlling an automated car washing system with four working modes and implemented with a custom mode option is given. The resulting compact design minimizes power consumption and effectively addresses other major issues. These comprehensive optimizations meet stringent performance, area, and power requirements, elevating the operational efficiency of automated car washing systems. Furthermore, the design is synthesized and implemented using Xilinx's ISE Design Suite.

Keywords: ISE Design Suite

# I. INTRODUCTION

Car washing is a critical aspect of vehicle maintenance, preventing rust, oxidation, and fine scratches, which can degrade the vehicle's appearance and longevity. Traditional car washing methods, while effective often involve high water consumption, substantial manual labor, and inconsistent cleaning quality. As the need for more efficient and sustainable solutions grows, modern car wash systems have evolved into automated, contact-based, and touch-free options, offering a variety of programs such as prewashing, waxing, drying, and polishing. Despite these advancements, existing systems still face challenges, including high operational costs, inefficiency in integrating new technologies, and increased system complexity.

Automation has emerged as a solution to these challenges, providing efficient, eco-friendly, and high-quality car washing. Technologies like Field- Programmable Gate Arrays (FPGAs) offer an ideal platform for implementing such systems. FPGAsallow for flexible, reconfigurable designs that can be updated with minimal effort, leading to reduced resource consumption and improved performance. These systems can offer different modes for car washing, such as prewashing, water washing, waxing, drying, and inspection, ensuring a more personalized and thorough cleaning process. However, traditional systems often lack the flexibility to easily incorporate new features or technologies.

The motivation for this project arises from the growing demand for more sustainable, efficient, and customizable car washing solutions. Traditional methods consume too much water, are labour- intensive, and often fail to meet modern environmental standards. To address these issues, this project proposes an FPGA-based automated car washing system designed using Verilog HDL. The main objectives are to develop a system that optimizes power, area, and timing for greater efficiency, and to validate the system's functionality through simulations and implementation on Spartan-6 FPGA hardware. The goal is to deliver a scalable, eco- friendly, and efficient solution that improves both performance and customer satisfaction while minimizing resource consumption.

Copyright to IJARSCT www.ijarsct.co.in

Volume 5, Issue 10, June 2025

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Impact Factor: 7.67

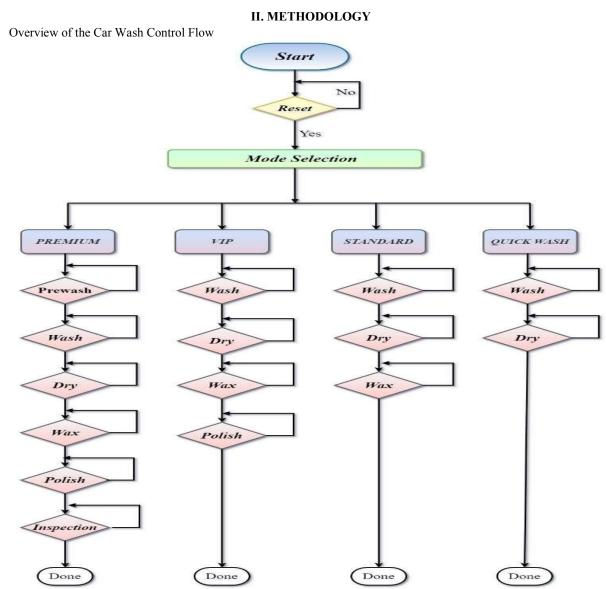

Fig.1. A control flowchart of the car washing system

The car washing system supports four modes:

- 1. VIP

- 2. Extra Foam

- 3. Standard

- 4. Low Cost

Mode Switching:

The system requires stopping the current mode before activating a new one. This ensures the process is sequential and avoids conflicts

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-28821

112

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 5, Issue 10, June 2025

Key Operational States for All Modes:

### 1. Foaming:

o Foam is sprayed over the car to ensure complete coverage.

o Foam is applied using nozzles around the vehicle.

# 2. Washing:

o Foam is stopped, and clean water is supplied to rinse the vehicle thoroughly.

# 3. Waxing:

o A layer of wax is applied to protect the car's surface.

### 4. Drying:

o Blow valves activate for a short duration to dry the vehicle.

### 5. Finishing:

o Concludes the process and resets the system, preparing it for the next operation.

### Control Mechanism:

- The Ready Block:

- o Monitors various system parameters, such as:

- $\Box$  User input for mode selection.

- $\Box$  Presence of foam, wax, or alarms.

- o It ensures the system's readiness before starting or switching processes.

- Sequential Operation:

o Each mode progresses through the same steps(Foam  $\rightarrow$  Water  $\rightarrow$  Wax  $\rightarrow$  Dry  $\rightarrow$  Finish) but may differ in intensity or application level based on the mode chosen (e.g., more foam for "Extra Foam" mode).

# **III. IMPLEMENT DESIGN**

The Car Washing System module uses a finite state machine (FSM) to control the various phases of the car wash process based on the selected mode. The FSM transitions between states (IDLE, PRE\_WASH, WASH, DRY, WAX, POLISH, INSPECTION, COMPLETE) and controls output signals (prewash, washing, drying, waxing, polishing, inspection, done) according to mode- specific time durations.

#### **Inputs:**

• clk: Clock signal to synchronize state transitions.

• reset: Resets the FSM.

• mode\_select: 3-bit input to select the car wash mode (VIP, Standard, Quick, Premium).

#### **Outputs:**

• Signals for each phase (pre\_wash, washing, drying, waxing, polishing, inspection, done).

# **Internal Registers:**

• Parameters define the duration for each phase, encoded in clock cycles (e.g., t1, t2, t3, etc.).

Time Duration Parameters:

Each phase is assigned a specific time duration in clock cycles:

• t1:200cycles

• t2:300cycles

Copyright to IJARSCT www.ijarsct.co.in

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 5, Issue 10, June 2025

- t3:400cycles

- t4:500cycles

- t5:600cycles

- t6:200cycles

- t7:100cycles

Mode-specific Time Durations:

• VIP Mode(3'b001):

o No pre-wash, wash for t1 (200 cycles), dry for t2 (300 cycles), wax for t3 (400 cycles), polish for t4 (500 cycles), no inspection.

The time durations for each phase are set based on the selected mode, ensuring that each phase lasts the designated number of clock cycles.

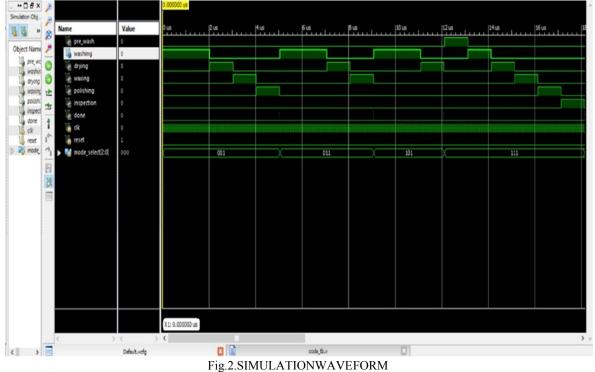

# IV. SIMULATION RESULT

The fig 2 shows the behaviour of a multi-stage process over time, with specific control signals for each stage (prewash, washing, drying, waxing, polishing, inspection, done). The clock (clk) signal provides the timing reference, while the reset signal initializes the system. Initially, the reset signal is high, keeping all stages inactive. When the mode\_select[2:0] bus changes from 000 to 111, activating the pre\_wash ,washing ,waxing, polishing, and inspection stages sequentially. The done signal indicate the end of the entire process .This process will repeat to all the other modes which will activate there respective states.

Copyright to IJARSCT www.ijarsct.co.in

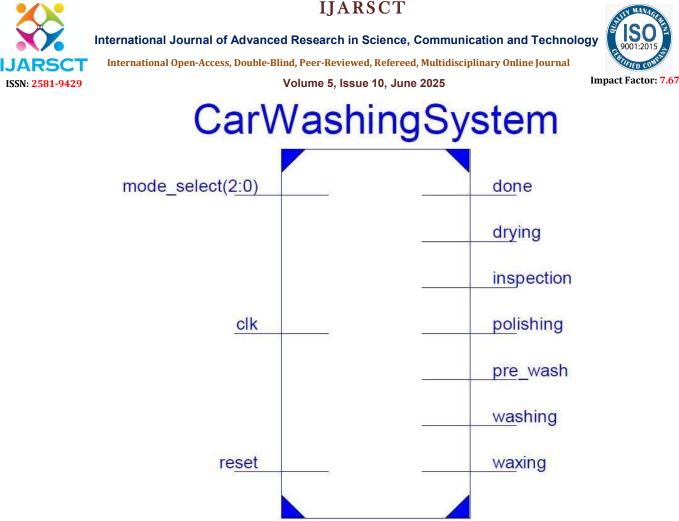

Fig. 3. Model of the car washing system

Fig. 3 shows the top module of the design for the automated car washing system. The top module is a crucial component that acts as the gateway for inputs and outputs, as well as managing the internal operations of the processor. A processor is a device that executes a series of instructions to carry out specific tasks.

Copyright to IJARSCT www.ijarsct.co.in

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 5, Issue 10, June 2025

| A                                                 | 8               | C        | D       | E          | F             | G            | н               | 1 | 1      | ĸ         | L           | М                                                                                                              | N           |

|---------------------------------------------------|-----------------|----------|---------|------------|---------------|--------------|-----------------|---|--------|-----------|-------------|----------------------------------------------------------------------------------------------------------------|-------------|

| Device                                            |                 |          | On-Chip | Power (W)  | Used          | Available    | Ltilization (%) |   | Supply | Summary   | Total       | Dynamic                                                                                                        | Quescent    |

| Family                                            | Splartan6       |          | Clocks  | 0.000      | 1             | -            | -               |   | Source | Votage    | Current (A) | Current (A)                                                                                                    | Current (A) |

| Part                                              | xc6abx9         |          | Logic   | 0.000      | 38            | 5720         | 1               |   | Vocine | 1.200     | 0.004       | the second s |             |

| Package                                           | tigg144         |          | Signals | 0.000      | 52            | -            | -               |   | Vocaux | 2.500     | 0.003       | 0.000                                                                                                          | 0.003       |

| Temp Grade                                        | C-Grade         | Q.       | KOs     | 0.000      | 12            | 102          | 12              |   | Vcco25 | 2.500     | 0.001       | 0.000                                                                                                          | 0.001       |

| Process                                           | Typical         | 9        | Leakage | 0.014      |               |              |                 |   |        |           |             |                                                                                                                |             |

| Speed Grade                                       | 2               |          | Total   | 0.014      |               |              |                 |   | î.     |           | Total       | Dynamic                                                                                                        | Quescent    |

|                                                   |                 |          |         |            |               |              |                 |   | Supply | Power (W) | 0.014       | 0.001                                                                                                          | 0.014       |

| Environment                                       |                 |          |         |            | Effective TJA | Max Anthient | Junction Temp   |   |        |           |             |                                                                                                                |             |

| Aribient Temp (C)                                 | 25.0            |          | Themai  | Properties | (C/W)         | (5)          | (2)             |   |        |           |             |                                                                                                                |             |

| Use custom TJA?                                   | No              | Y        |         |            | 38.4          | 84.4         | 25.6            |   |        |           |             |                                                                                                                |             |

| Custom TJA (C/W)                                  | NA              |          |         |            |               |              |                 |   |        |           |             |                                                                                                                |             |

| Artiow (LFM)                                      | 0               | V        |         |            |               |              |                 |   |        |           |             |                                                                                                                |             |

| Heat Sink                                         | None            | v        |         |            |               |              |                 |   |        |           |             |                                                                                                                |             |

|                                                   | ALLA .          |          |         |            |               |              |                 |   |        |           |             |                                                                                                                |             |

| Custom TSA (C/W                                   | 1064            | <u> </u> |         |            |               |              |                 |   |        |           |             |                                                                                                                |             |

| Custom TSA (C/W                                   | 100             |          |         |            |               |              |                 |   |        |           |             |                                                                                                                |             |

| Custom TSA (C/W<br>Characterization<br>Production | v1.3.2011-05-04 | -        |         |            |               |              |                 |   |        | _         |             |                                                                                                                |             |

### Figure 4. Power Report

Figure 4 gives an estimation of the power, which is 0.014 W.

All values displayed in nanoseconds (ns)

```

Timing constraint: Default period analysis for Clock 'clk'

Clock period: 5.016ns (frequency: 199.362MHz)

Total number of paths / destination ports: 238 / 19

----

Delay:

5.016ns (Levels of Logic = 4)

Source:

timer_6 (FF)

state FSM FFd1 (FF)

Destination:

clk rising

Source Clock:

Destination Clock: clk rising

Data Path: timer_6 to state_FSM_FFdl

Net

Gate

Delay

Delay Logical Name (Net Name)

Cell:in->out

fanout

timer_6 (timer_6)

state FSM FFde-In1_SW0 (N01)

state_FSM_FFde-In21 (state_FSM_FFde-In2)

state_FSM_FFd1-In1 (state_FSM_FFd1-In1)

state_FSM_FFd1-In3 (state_FSM_FFd1-In)

FDC:C->Q

0.525

0.954

2

LUT4:11->0

0.235

4

0.912

0.876

LUT6:14->0

6

0.250

LUT6:15->0

1

0.254

LUT6:IS->0

1

0.254

0.000

FDC:D

0.074

state_FSM_FFd1

5.016ns (1.592ns logic, 3.424ns route)

(31.7% logic, 68.3% route)

Total

```

Figure 5. Delay Analysis of the Design

Figure 5 gives an estimation of delay analysis, which is 5.01 ns for the design of the automatic car washing system.

Copyright to IJARSCT www.ijarsct.co.in

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 5, Issue 10, June 2025

Device Unlin 11 Slice Logic Utilization Durd Available Utilization Nintp(+) Number of Silce Registers 29 11.440 1% Number used as Flip Flops 19 Number used as Latches 5 Number used as Letch-thrus 0 Number used as AND/OR logics 0 riber of Size LUTe 36 \$.720 1% Number used as logic 37 5.728 1% 17 Number using O6 output only 10 Number using OS output only Number using OS and O6 30 Number used as ROM 8 Number used as Memory 0 1,440 0% Number used exclusively as nuts-thrus 1 Number with same-slice register load 6 Number with same-size carry load 1 Number with other load 5 Number of occupied Silces 12 1,430 1% Number of MUXCVs used 12 2,660 1% sumber of CUT Fig Flop pars used 38 25 Number with an unused Flip Flop 38 65% Number with an unused LUT 0 38 0% Number of fully used LUT-FF pairs 13 38 34% Number of unique control sets 1 Number of slice register step lost to control set restrictions 5 11,440 1% Number of bonded 2080 12 107 1246

Figure 6. Area Consumption from Design Summary

Figure 6 gives an estimation of the area used by the design of the automated car washing system.

| , 0                       |                  | 5 0       | 0 5  |           |  |

|---------------------------|------------------|-----------|------|-----------|--|

|                           | Existing Project |           |      | d Project |  |

|                           | Used             | Available | Used | Available |  |

| LUTs as Logic             | 34               | 53200     | 38   | 5720      |  |

| LUTs as memory            | 0                | 17400     | 0    | 1440      |  |

| Slice Registers           | 23               | 106400    | 19   | 11440     |  |

| Registers as<br>flipflops | 23               | 106400    | 19   | 11440     |  |

| Slice LUTs                | 34               | 53200     | 38   | 5720      |  |

Figure 7. The area comparison between the existing and proposed project

# **IV. CONCLUSION**

In the future, the automated car washing systems will be increasingly used as they combine a number of advantages such as saving time and money, easily operated system, profitability, rapid washing process, high-quality cleaning of hard-to-reach places such as grille, wheels and others and others. The complex programmable logic devices and field programmable gate array are widely used in the modern world. They are a modern and promising way in the design of various electromechanical objects and systems. Based on the developed flow chart of the proposed car washing system, the control program has been designed in ISE Design Suite software though the language Verilog HDL. The

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-28821

117

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 5, Issue 10, June 2025

implemented control allows a choice of four regimes depending on the money placed and the method of washing. The obtained simulation tests for the individual operating modes of the carwashing system prove the operability of the design model

### REFERENCES

[1] G. Subramanian, K. Tharani, Raja, K. Gowtham Babu and T. Devashena, "Simulation of Automatic Car Washing Using PLC", - International Journal for Scientific Research & Development, Vol. 3, No. 01, pp.438-439,2015.

[2] K. Vidyasagar, R. Prasad and P. Nagasekhar, "RFID-GSM Autonomous Car Washing System", International Journal of Computer Applications, Vol. 121, No.2, pp. 30-33, 2015.

[3] Y. Yu, L. Kurnianggoro and K.-H. Jo, "Design of intelligent car washing system", Conference: 201554th Annual Conference of the Society of Instrument and Control Engineers of Japan (SICE), 2015.

[4] Z. Lalluwadia, N. Bhatia and J. Rana, "Automatic carwashingsystemusingPLC", International Journal of Innovative Research in Technology, Vol.3, No.9, pp. 40-43, 2017.

[5] M. Thwe, H. Min and N. New, "Programmable Logic Controller based Automatic Car Washing System", Iconic Research and Engineering Journals, Vol. 2, No.11, pp. 1-7, 2019.

[6] K. Akilandeswari, J. Haripriya, S. Nirmala and R. Prabha, "Implementation of Smart Car WashingUsing GSM PLC", International Journal ofInnovative Research in Science, Engineering and Technology, Vol. 3, No.3, pp. 10006-10013, 2014.

[7] H. Janik, A. Kupiec, "Trends in modern car washing", Polish Journal of Environmental Studies, Vol. 16, No. 6, pp. 927-931, 2007.

[8] T. Pinjari, M. Hadpad, D. Sukale, D. Mulgoankar and P. Aswar, "Automatic Car Washing Systemusing Microcontroller", International ResearchJournal of Engineering and Technology, Vol. 7, No.6, pp. 2711-2714, 2020.

[9] R. Singh, S. Nigam, S. Aggrawal, M. Neelgar, S. Kaura and Kailash Sharma, "Design and implementation of automatic car washing systemusing PLC", International Research Journal of Engineering and Technology, Vol. 5, No.5, pp. 4183-4185, 2018.

[10] V. Taraate, Digital Logic Design using Verilog - Coding and RTL Synthesis, Springer India, 2016.

[11] P. Chu, FPGA Prototyping by Verilog Examples, John Wiley & Sons, Inc, 2008.

[12] S. Brown and Z. Vranesic, Fundamentals of Digital Logic with VHDL Design, The McGraw-Hill Companies, 2009.

[13] B. Zeidman, Designing with FPGAs and CPLDs, 2002.

[14] B. Patil, R. Henry and A. Patwardhan, "Training methodology: Complex programmable logic device based system design & implementation", 2nd International Conference on Education and New Learning Technologies, pp. 1995-1998, 2010.

[15] S. Ramachandran, Digital VLSI Systems Design, Springer, 2007.