International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 5, Issue 12, April 2025

# Inference Workloads in Real-Time Systems: Optimizing Performance

Deepika Bhatia

Abstract: This article examines the optimization strategies for inference workloads in real-time systems across various performance-critical applications. As artificial intelligence becomes increasingly embedded in time-sensitive domains, the need for efficient execution of inference tasks under strict latency constraints has become paramount. Unlike training processes prioritizing accuracy regardless of computational cost, inference workloads must balance precision with performance constraints, particularly in resource-limited environments. The article explores three key optimization approaches: reduced precision computing techniques that preserve accuracy while decreasing computational demands, resource allocation and workload management strategies that adapt to fluctuating conditions, and specialized cache architectures that minimize memory access latencies for tensor operations. Through case studies in autonomous vehicles, industrial automation, and financial transaction monitoring, the article demonstrates how these optimizations enable mission-critical AI systems to meet stringent real-time requirements. Additionally, emerging directions, including hardware-software co-design, neural architecture search for efficiency, and sparse computation, are explored as promising frontiers for future optimization efforts

**Keywords:** Real-time inference, reduced precision computing, resource allocation, memory optimization, hardware-software co-design

### I. INTRODUCTION

In today's rapidly evolving technological landscape, real-time AI inference has become critical across numerous industries. The global AI accelerator market size was valued at USD 34.8 billion in 2023 and is expected to expand at a compound annual growth rate (CAGR) of 29.8% from 2024 to 2030, with cloud inference generating the largest revenue share at over 61% of the market [1]. This growth reflects the increasing deployment of AI systems in time-sensitive domains where decision-making must occur within milliseconds—from autonomous vehicles making split-second decisions to financial systems detecting fraudulent transactions as they occur.

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-25987

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 5, Issue 12, April 2025

Real-time inference presents unique technical challenges that differ significantly from training workloads. While training focuses on optimization for accuracy regardless of computational cost, inference must balance precision with strict performance constraints. According to industry analyses, latency and throughput requirements vary significantly across applications, with edge devices facing particular challenges due to limited computational resources. Inference workloads must be optimized for the specific hardware they run, with GPUs remaining the dominant hardware accelerator due to their parallel processing capabilities and mature software ecosystem [2]. The deployment environment significantly impacts performance, with factors such as memory bandwidth, thermal constraints, and power availability all influencing the optimization approach.

This article explores key optimization strategies enabling these performance-critical systems to operate efficiently under stringent real-time constraints. We examine reduced precision computing techniques that maintain accuracy while decreasing computational demands. These intelligent resource allocation mechanisms adapt to fluctuating workloads and specialized cache architectures designed to minimize memory access latencies for common tensor operations. These approaches collectively address the fundamental challenges of inference deployment, allowing systems to meet their performance requirements within power and cost constraints.

### **II. THE CHALLENGE OF REAL-TIME INFERENCE**

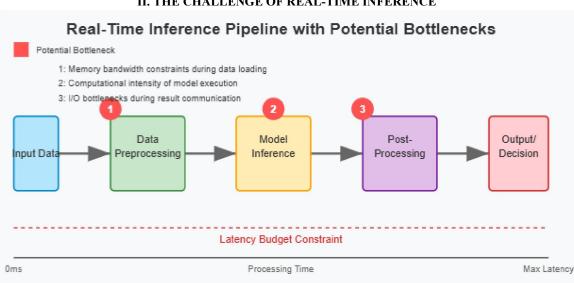

Real-time inference presents unique challenges compared to traditional batch processing. Systems must deliver results within strict time boundaries-often measured in milliseconds or microseconds-while maintaining accuracy and reliability. Research on sensor-based autonomous systems shows that real-time inference for embedded AI must often operate under severe resource constraints, with some applications requiring complete inference cycles in under 30ms to maintain operational safety. The balance between model complexity and inference speed presents a fundamental challenge, as studies of convolutional neural networks demonstrate that deeper architectures with more parameters typically achieve higher accuracy but at the cost of increased latency [3]. This trade-off becomes particularly critical in edge-computing scenarios with limited computational resources.

The financial sector exemplifies the extreme demands of low-latency inference, particularly in high-frequency trading applications. Machine learning models must process market data and make trading decisions in microseconds rather than milliseconds. Competitive advantages in this domain are measured in nanoseconds, with specialized hardware implementations often required to achieve sub-microsecond inference latency. Integrating these ultra-low latency ML pipelines with existing high-frequency trading infrastructure introduces additional complexity, requiring careful optimization of the entire system architecture to minimize end-to-end latency [4]. Any delay in processing can lead to

**Copyright to IJARSCT** www.ijarsct.co.in

DOI: 10.48175/IJARSCT-25987

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

### Volume 5, Issue 12, April 2025

catastrophic consequences in safety-critical applications or significant financial losses in business contexts, making optimization of these workloads essential for practical deployment.

The computational complexity of modern deep learning models further compounds these challenges. State-of-the-art vision transformers can contain over 600 million parameters, requiring significant memory bandwidth and computational resources. When deployed in resource-constrained environments such as edge devices, these models must be optimized through pruning and quantization without sacrificing accuracy. Power consumption represents another critical constraint, particularly for battery-powered devices. The energy efficiency of inference operations, measured in inferences per joule, has become a key performance indicator alongside raw throughput.

### **III. KEY OPTIMIZATION STRATEGIES**

### **3.1 Reduced Precision Computing**

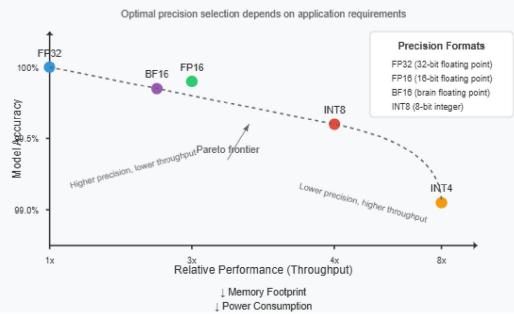

One of the most effective approaches to accelerating inference workloads is the strategic reduction of computational precision. Traditional deep learning models trained with 32-bit floating-point (FP32) precision can often be optimized for inference using lower precision formats without significant accuracy degradation. Research demonstrates that INT8 quantization on deep learning models can improve up to 4x throughput with less than 1% accuracy loss when properly calibrated [5]. This approach is particularly valuable for inference, where computational efficiency often precedes numerical precision.

INT8 quantization converts floating-point values to 8-bit integers, enabling models to achieve up to 4x reduction in memory bandwidth requirements and significantly faster computation times. Modern quantization techniques preserve accuracy through calibration processes that minimize information loss during precision reduction. TensorRT's INT8 calibration uses the KL divergence algorithm to determine optimal scaling factors for each tensor, ensuring minimal information loss during quantization.

### Precision vs. Performance Tradeoff for Inference

FP16 (half-precision) balances INT8 and FP32, substantially reducing memory footprint while preserving numerical flexibility for operations sensitive to rounding errors. The research found that mixed-precision models using FP16 can improve up to 3x performance over pure FP32 implementations when utilizing specialized hardware like NVIDIA Tensor Cores [6]. Their research also revealed that while mixed-precision computation introduces some numerical

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-25987

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

### Volume 5, Issue 12, April 2025

differences, these differences typically remain below 1% for well-designed neural network architectures, making them negligible for most inference applications.

The key insight driving reduced precision techniques is that inference tasks often don't require the same numerical precision as training processes. By carefully analyzing accuracy-performance tradeoffs, engineers can substantially accelerate inference while maintaining acceptable accuracy levels for specific applications.

### 3.2 Resource Allocation and Workload Management

Efficient resource allocation represents another critical dimension of inference optimization. Dynamic core allocation enables modern AI inference chips and accelerators to implement sophisticated load-balancing algorithms that distribute computational workloads across available processing elements. This approach ensures that processing resources are utilized optimally even under fluctuating workload conditions, with adaptive scheduling mechanisms adjusting resource allocation based on real-time performance metrics and system load.

Workload prioritization mechanisms ensure that time-critical inference tasks receive computational resources ahead of less urgent operations. This is particularly important in mixed-criticality systems where some inference tasks have strict real-time requirements while others can tolerate longer processing times. Research has demonstrated that priority-aware scheduling can reduce worst-case latency for critical inference tasks by up to 47% compared to non-prioritized approaches, making it essential for applications with heterogeneous performance requirements.

Pipeline parallelism breaks inference tasks into stages that can execute concurrently on different processing elements, helping maximize throughput while potentially reducing end-to-end latency. Modern inference accelerators implement sophisticated pipelining techniques that overlap communication with computation, hiding memory access latencies behind useful computational work. This approach is particularly effective for large models that cannot fit entirely in on-chip memory, allowing different network layers to be processed simultaneously on different compute units.

### 3.3 Cache Architecture and Memory Optimization

Memory access patterns significantly impact inference performance, often becoming the primary bottleneck in real-time systems. Specialized cache hierarchies optimized for common tensor operations can dramatically reduce memory access latencies. These include tensor-aware prefetching mechanisms and specialized data layouts that maximize spatial and temporal locality. Some designs achieve memory bandwidth utilization improvements of up to 85% for common convolutional neural network workloads.

Memory fusion techniques combine multiple tensor operations to minimize data movement between memory and compute units, reducing the memory bandwidth bottleneck that often limits inference performance. This approach is particularly valuable for operations with producer-consumer relationships, where the output of one operation serves as the input of another. By fusing these operations, intermediate results can remain in high-speed cache or register files rather than being written to and subsequently read from main memory.

On-chip memory optimization ensures that frequently accessed weights and activations remain close to computational units, minimizing expensive off-chip memory accesses. This requires careful model architecture and analysis of access patterns to identify the most performance-critical parameters and intermediate values. Techniques such as weight pruning and sparsity exploitation can further reduce memory requirements, allowing more of the model to fit within the limited on-chip memory resources available in most inference accelerators.

### IV. REAL-WORLD APPLICATIONS

These optimization techniques enable mission-critical AI systems across multiple domains, demonstrating their practical impact on performance-sensitive applications:

#### 4.1 Autonomous Vehicles

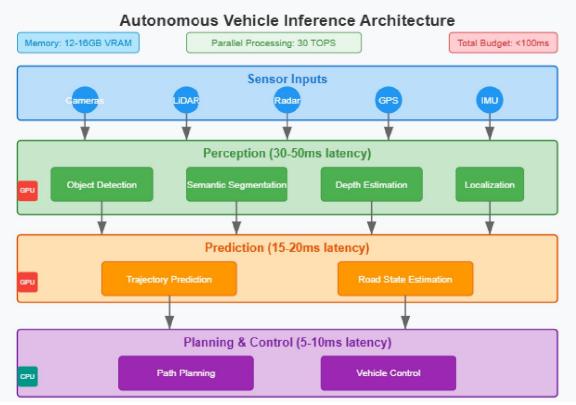

Self-driving vehicles must process sensor data and make driving decisions within milliseconds. Modern autonomous driving platforms integrate multiple deep neural networks for perception, prediction, and planning—all of which must operate under strict latency constraints. Research shows that autonomous vehicles typically generate between 1.4 to 19

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-25987

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

### Volume 5, Issue 12, April 2025

terabytes of data per hour from various sensors, including cameras, LiDAR, and radar, requiring on-vehicle inference systems capable of processing this information in real time [7]. Optimized inference workloads enable these systems to detect objects, predict movements, and plan trajectories with the latency constraints necessary for safe operation at highway speeds.

The performance requirements for autonomous vehicle perception systems are particularly demanding, with object detection and segmentation models requiring inference times under 50ms to support safe operation at highway speeds. By implementing precision reduction strategies and specialized memory architectures, automotive-grade inference processors have achieved up to 30 TOPS (trillion operations per second) while maintaining power consumption below 10 watts. This performance envelope enables sophisticated AI models to run in real-time without exceeding in-vehicle computing platforms' thermal and power constraints.

### 4.2 Manufacturing and Industrial Automation

Predictive maintenance systems in manufacturing environments continuously monitor equipment performance using real-time inference to detect anomalies before they lead to failures. These systems analyze sensor data streams from industrial equipment to identify patterns indicative of impending failures, enabling proactive maintenance interventions. Implementation of optimized inference at the edge has demonstrated significant improvements in anomaly detection latency, with some deployments reducing detection time from minutes to sub-second levels [8].

Industrial IoT deployments typically feature distributed inference capabilities, with initial filtering and anomaly detection performed directly on sensors or gateway devices, followed by more sophisticated analysis on edge servers. This hierarchical approach requires inference optimization techniques tailored to each level of the processing pipeline. Extreme quantization and model compression at the sensor level enables inference on microcontroller-class devices with as little as 256KB of RAM. More sophisticated techniques, including pipeline parallelism and dynamic resource

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-25987

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 5, Issue 12, April 2025

allocation, ensure efficient processing of aggregated data streams from multiple sources at the gateway and edge server levels.

### 4.3 Financial Transaction Monitoring

Financial institutions deploy real-time inference systems to monitor transactions for fraudulent activity. These systems must process immense transaction volumes with minimal latency to enable intervention before fraudulent transactions are completed. Major financial institutions can process over 10,000 transactions per second during peak periods, requiring inference systems capable of sub-millisecond response times to maintain acceptable overall latency.

The optimization challenges in financial transaction monitoring are compounded by integrating multiple model types including classical machine learning algorithms, deep neural networks, and rule-based systems—into cohesive decision pipelines. Heterogeneous inference optimization techniques that allocate different components of the processing pipeline to the most appropriate hardware resources have shown particular promise in this domain. Studies have demonstrated that properly optimized fraud detection systems can achieve detection rates exceeding 95% while maintaining false positive rates below 1%, even when operating under the strict latency constraints required for realtime transaction processing.

### **V. FUTURE DIRECTIONS**

As real-time inference demands continue to increase, several emerging approaches show promise for further optimization:

### 5.1 Hardware-Software Co-Design

Tighter integration between model architecture design and hardware acceleration capabilities enables optimizations that wouldn't be possible with either approach alone. Traditional development pipelines where models are designed without consideration for target hardware frequently result in suboptimal performance. The co-design approach treats the model architecture and hardware implementation as a unified optimization problem, allowing for simultaneous design space exploration. Recent research on neural architecture search for secure inference demonstrates that hardware-aware design approaches can yield substantial improvements in latency-security tradeoffs compared to conventional implementation methodologies [9].

Co-design methodologies incorporate hardware constraints directly into the model development process. For example, when evaluating candidate architectures, neural architecture search algorithms can be augmented with hardware-aware cost models that consider factors such as memory bandwidth, computation patterns, and energy consumption. This approach has led to specialized neural network architectures that map efficiently to specific accelerator designs while maintaining competitive accuracy. The increasing adoption of domain-specific languages and compilers for AI further enables this integration by providing abstractions that allow model developers to express computation in ways that hardware designers can efficiently implement.

#### 5.2 Neural Architecture Search for Efficiency

Automated techniques that discover model architectures optimized specifically for inference performance rather than just accuracy have shown remarkable promise. Traditional neural network architectures are designed manually through iterative experimentation, focusing primarily on accuracy metrics. In contrast, neural architecture search (NAS) employs algorithmic approaches to explore the design space, identifying architectures that balance accuracy with inference efficiency.

Efficiency-focused NAS directly incorporates latency, throughput, memory footprint, and energy consumption into the optimization objective. The EfficientNet approach introduced by Tan and Le demonstrates that carefully balancing network depth, width, and resolution can lead to models that achieve state-of-the-art accuracy while up to 8.4x smaller and 6.1x faster than previous convolutional neural networks [10]. Their compound scaling method systematically addresses the relationship between different network dimensions, resulting in a family of models that efficiently scale across a wide range of resource constraints. The automation aspect of NAS is particularly valuable as model complexity

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-25987

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

#### Volume 5, Issue 12, April 2025

increases, allowing exploration of architectural choices that human designers might overlook. Recent advances in NAS techniques have dramatically reduced the computational resources required for architecture exploration, making these approaches increasingly practical for production deployment.

### 5.3 Sparse Computing

Leveraging sparsity in activation maps and weight matrices to skip unnecessary computations represents one of the most promising frontiers in inference optimization. Both trained sparsity, where models are explicitly optimized to contain numerous zero values, and dynamic sparsity, where zeros emerge naturally during inference, can be exploited to reduce computational workload. Hardware architectures designed to capitalize on sparsity patterns can achieve effective speedups proportional to the sparsity rate, potentially reducing computational requirements by 70-90% for models with high sparsity.

Sparse computing encompasses various techniques, including network pruning, where less important connections are systematically removed; structured sparsity, where entire channels or filters are eliminated; and dynamic activation pruning, where intermediate feature maps are thresholded during inference. These approaches are particularly valuable for edge deployment where computational resources are severely constrained. The combination of model sparsification with specialized hardware support for sparse tensor operations presents one of the most promising pathways toward enabling increasingly complex models to operate within the strict performance constraints of real-time systems.

### **VI. CONCLUSION**

The optimization of inference workloads for real-time systems represents a multifaceted challenge spanning hardware architecture, system software, and machine learning model design. These optimization techniques become increasingly crucial as AI applications increasingly transition from cloud environments to edge devices with strict latency requirements. The strategic application of reduced precision computing balances computational efficiency with accuracy, while intelligent resource allocation ensures optimal utilization under varying workload conditions. Memory optimization approaches address bandwidth limitations that often constrain inference performance in resource-constrained environments. These complementary strategies collectively enable engineers to develop real-time AI systems that meet demanding performance requirements across diverse application domains. Looking forward, the continued evolution of hardware-software co-design methodologies, efficiency-focused neural architecture search, and sparse computing techniques promises to enhance the capabilities of real-time inference systems further, opening new possibilities for AI deployment in increasingly challenging operational contexts.

#### REFERENCES

[1] Grand View Research, "AI Accelerator Market Size, Share & Trends Analysis Report By AI Accelerator Types (GPUs, TPUs), By Technology Integration, By End-use (IT & Telecom, Automotive), By Region, And Segment Forecasts, 2024 - 2030," Grand View Research. [Online]. Available: <u>https://www.grandviewresearch.com/industry-analysis/ai-accelerator-market-report</u>

[2] Spot.io, "Understanding AI inference: Challenges and best practices," Spot.ai. [Online]. Available: https://spot.io/resources/ai-infrastructure/understanding-ai-inference-challenges-and-best-practices/

[3] Jelena Kocić et al., "An End-to-End Deep Neural Network for Autonomous Driving Designed for Embedded Automotive Platforms," Sensors 2019. [Online]. Available: <u>https://www.mdpi.com/1424-8220/19/9/2064</u>

[4] Xelera Technologies, "Low-latency Machine Learning Inference for High-Frequency Trading," LinkedIn, 2023. [Online]. Available: <u>https://www.linkedin.com/pulse/low-latency-machine-learning-inference-high-frequency</u>

[5] Szymon Migacz, "8-bit Inference with TensorRT," NVIDIA Corporation, 2017. [Online]. Available: https://www.cse.iitd.ac.in/~rijurekha/course/tensorrt.pdf

[6] Stefano Markidis et al., "NVIDIA Tensor Core Programmability, Performance & Precision," arXiv:1803.04014, 2018. [Online]. Available: <u>https://arxiv.org/abs/1803.04014</u>

[7] Shaoshan Liu et al., "Computer Architectures for Autonomous Driving," IEEE Computer, Volume 50, Issue 8, 2017. [Online]. Available: <u>https://ieeexplore.ieee.org/document/7999133</u>

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-25987

International Journal of Advanced Research in Science, Communication and Technology

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 5, Issue 12, April 2025

[8] Rui Zhao et al., "Deep learning and its applications to machine health monitoring," Mechanical Systems and Signal Processing, Volume 115, 15 January 2019. [Online]. Available: https://www.sciencedirect.com/science/article/abs/pii/S0888327018303108

[9] Weiwen Jiang et al., "Hardware/Software Co-Exploration of Neural Architectures," arXiv:1907.04650, 2020. [Online]. Available: <u>https://arxiv.org/abs/1907.04650</u>

[10] Mingxing Tan and Quoc V. Le, "EfficientNet: Rethinking Model Scaling for Convolutional Neural Networks," arXiv:1905.11946, 2020. [Online]. Available: <u>https://arxiv.org/abs/1905.11946</u>

Copyright to IJARSCT www.ijarsct.co.in