International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Volume 4, Issue 2, August 2024

# Neuromorphic Computing: Innovations and Future Prospects

## Panja Naga Laxmi

Assistant Professor, Department of Computer Science Aurora PG College, RTC Cross Roads, Hyderabad, India nagalaxmipanjai@gmail.com

Abstract: This review aims to provide a comprehensive analysis of neuromorphic computing, a novel brain-inspired paradigm designed to address the limitations of traditional computing architectures, particularly those associated with Moore's law memory wall phenomenon. Neuromorphic computing is an innovative field that emulates the neural structures and processing capabilities of biological brains to enhance computational performance and energy efficiency. This review explores the various projects and methodologies developed in both industry and academia, focusing on digital, analog, and hybrid systems, as well as on-chip and external learning mechanisms. It examines different neuromorphic chip architectures and their implementation of spiking neural networks (SNNs), which facilitate parallel and asynchronous data processing similar to biological neural activity. The review addresses the challenges inherent in current systems, such as memory integration complexities and data exchange inefficiencies. Additionally, it proposes future directions, including the integration of quantum computing principles, to further advance neuromorphic computing technology and overcome existing limitations, aiming to achieve greater performance and energy efficiency

**Keywords:** neuromorphic computing architecture; spiking neu-ral networks; non-Von Neumann computer; brain-inspired chip; artificial intelligence; machine learning.

## I. INTRODUCTION

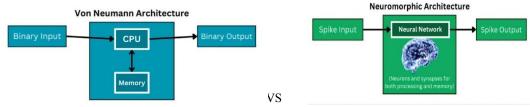

Artificial Intelligence (AI) is a rapidly advancing field that spans a wide range of applications and technologies. Traditional computing architectures, such as the Von Neumann model, face significant limitations in handling complex AI algorithms due to their high-power consumption and associated carbon emissions. The Von Neumann architecture relies on a central processing unit (CPU) and memory units that operate sequentially, which has become increasingly inefficient as the demands for computing power and memory bandwidth have grown. As noted, training a single deep learning model can consume as much energy as the lifetime carbon footprint of five cars, highlighting the urgent need for more energy-efficient computing solutions. The limitations of Moore's law, which once drove the rapid miniaturization of transistors to enhance performance, have led to a phenomenon known as the memory wall, where improvements in speed are not matched by corresponding gains in memory performance, thereby constraining overall system efficiency.

In response to these challenges, neuromorphic computing emerges as a promising alternative by emulating the brain's neural architecture. Unlike traditional Von Neumann systems, neuromorphic computing integrates artificial neurons and synapses to perform computations in a manner similar to biological brains, offering significant improvements in energy efficiency and computational capability. Neuromorphic chips utilize spiking neural networks (SNNs) which process information through discrete, time-dependent spikes rather than continuous values. This approach supports parallel and asynchronous processing, reducing power consumption and enhancing performance. The design of neuromorphic systems involves a variety of hardware implementation strategies, including analog, digital, and hybrid methods, each contributing to different aspects of performance and efficiency. This review delves into the various neuromorphic chip architectures, explores the implementation of different spiking neuron models, and discusses future directions, including the potential integration of quantum computing principles to further advance the field.

DOI: 10.48175/IJARSCT-19435

Copyright to IJARSCT www.ijarsct.co.in

397

#### International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Impact Factor: 7.53

Volume 4, Issue 2, August 2024

#### **Existing Proposal**

Neuromorphic chips are designed to mimic the functions of the human brain by using artificial neurons and synapses. The human brain, with its vast network of neurons and synapses communicating through electrical spikes, inspired these chips due to their efficiency in performing complex cognitive tasks while consuming minimal energy. Unlike traditional Von Neumann computers, which separate processing units and memory, neuromorphic chips integrate both functions within a network of neurons and synapses, operating in a parallel and asynchronous manner. This architecture allows neuromorphic systems to process information in a way that is more energy-efficient compared to the sequential, clock-driven approach of Von Neumann machines. Neuromorphic chips leverage several advantages including connectionism (neural networks that learn and solve problems through weight adjustments), parallelism (simultaneous neuron operation), and asynchrony (task-specific neuron activation). They also use impulse-based information transmission, allowing them to operate with lower power consumption by activating neurons only when necessary.

Spiking Neural Networks (SNNs) are employed in neuromorphic chips due to their ability to emulate biological neuronal processes. Unlike traditional Artificial Neural Networks (ANNs), which use continuous values and fixed activation functions, SNNs operate using spike signals and differential equations. This approach allows for energy-efficient and parallel data processing. SNNs use models like the integrate-and-fire, leaky integrate-and-fire, and Izhikevich models to simulate neural activity and communication through spikes. Hardware implementations of SNNs can be categorized into large-scale accelerators and low-power accelerators. Large-scale accelerators, such as SpiNNaker and True North, are designed for high throughput and scalability, while low-power accelerators, like those developed by Frenkel et al. and Zheng et al., focus on energy efficiency and accuracy for edge applications. These chips often incorporate specialized algorithms and models to optimize their performance and adapt to various tasks, demonstrating the versatility and potential of neuromorphic computing.

## **Proposed Method and Future Work**

Comparing the properties of each project, it is observed that in-memory computations have not been implemented using digital design as they require data exchange between the arithmetic logic unit (ALU) and memory cells, introducing complexities and added costs.

| Property              | TrueNorth                          | Loihi                                 |

|-----------------------|------------------------------------|---------------------------------------|

| In-memory computation | Near-memory                        | Near-memory                           |

| Signal                | Spikes                             | Spikes                                |

| Size neurons/synapses | 1 M/256 M                          | 128 K/128 M                           |

| On-device learning    | No                                 | STDP                                  |

| Analogue              | No                                 | No                                    |

| Eve n t - based       | Yes                                | yes                                   |

| nm                    | 28                                 | 14                                    |

| Features              | First industrial neuromorphic chip | First neuromorphic chip with training |

|                       | without training (IBM)             | (Intel)                               |

To address the limitations of existing neuromorphic computing systems, integrating more SRAM (Static Random Access Memory) has proven effective, as demonstrated by the Loihi and TrueNorth projects. By moving memory closer to the processing units, these systems reduce latency and improve performance.

One promising direction for enhancing neuromorphic computing is the development of a heterogeneous quantum neuromorphic computing system. Quantum computing leverages quantum mechanics principles enabling simultaneous

DOI: 10.48175/IJARSCT-19435

Copyright to IJARSCT www.ijarsct.co.in

398

2581-9429

**JARSCT**

#### International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Impact Factor: 7.53

### Volume 4, Issue 2, August 2024

parallel computations through qubits, which can exist in multiple states (0 and 1) due to superposition. This capability can enhance pattern recognition in neuromorphic systems while also potentially reducing overall power consumption. However, implementing quantum neural networks in hardware presents challenges. Precise control over connection strengths is crucial, and issues such as quantum coherence loss and large temperature variations need to be addressed to ensure reliable operation.

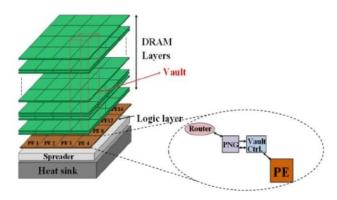

The NeuroTower features a 2D mesh-connected network-on-chip with stacked DRAM (Dynamic Random Access Memory) for 3D memory integration. This system employs programmable neurosequence generators to facilitate data retrieval between DRAM stacks and processing elements. Additionally, we have incorporated a pruning component to exploit sparsity and reduce network-on-chip traffic, thereby minimizing power consumption. The architecture includes multiple DRAM chips divided into partitions, with each partition connected to a processing element via high-speed through-silicon vias (TSVs). These DRAM stacks store all network information, including state and connectivity weights, allowing for efficient data movement and processing.

## II. CONCLUSION

Neuromorphic computing holds significant potential for replacing traditional Von Neumann computers, especially in executing complex algorithms. Its power efficiency and learning capabilities can greatly enhance system performance. Future research should focus on optimizing neuromorphic chips, improving learning techniques, and expanding their applications beyond single-use scenarios. Combining the NeuroTower architecture with quantum computing could create a flexible, high-performance computing system with substantial memory capacity, enhanced speed, and reduced energy consumption.

#### REFERENCES

- [1]. Luo, T., Wong, W.F., Goh, R.S.M., Do, A.T., Chen, Z., Li, H., Jiang, W., & Yau, W. (2023). Achieving Green AI with Energy-Efficient Deep Learning Using Neuromorphic Computing. *Communications of the ACM*, 66(7), 52–57. https://doi.org/10.1145/3588591

- [2]. Kumar, S., Wang, X., Strachan, J.P., Yang, Y., & Lu, W.D. (2022). Dynamical memristors for higher-complexity neuromorphic computing. *Nature Reviews Materials*, 7, 575–591. https://doi.org/10.1038/s41578-022-00434-z

- [3]. Xu, B., Huang, Y., Fang, Y., Wang, Z., Yu, S., & Xu, R. (2022). Recent Progress in Neuromorphic Computing Based on Silicon Photonics: Electronic–Photonic Co-Design, Device, and Architecture. *Photonics*, 9(10), 698. https://doi.org/10.3390/photonics9100698

- [4]. Schuman, C.D., Kulkarni, S.R., Parsa, M., Mitchell, J.P., Date, P., & Kay, B. (2022). Opportunities for neuromorphic computing algorithms and applications. *Nature Computational Science*, 2, 10–19. https://doi.org/10.1038/s43588-021-00184-y

- [5]. Byun, K., Choi, I., Kwon, S., Kim, Y., Kang, D., Cho, Y.W., Yoon, S.K., & Kim, S. (2022). Recent Advances in Synaptic Nonvolatile Memory Devices and Compensating Architectural and Algorithmic Methods Toward

Copyright to IJARSCT www.ijarsct.co.in

DOI: 10.48175/IJARSCT-19435

2581-9429

**JARSCT**

## International Journal of Advanced Research in Science, Communication and Technology (IJARSCT)

International Open-Access, Double-Blind, Peer-Reviewed, Refereed, Multidisciplinary Online Journal

Impact Factor: 7.53

## Volume 4, Issue 2, August 2024

- 2200884. Fully Integrated Neuromorphic Chips. Advanced Materials Technologies, 8(11), https://doi.org/10.1002/admt.202200884

- [6]. Javanshir, A., Nguyen, T.T., Mahmud, M.A.P., & Kouzani, A.Z. (2022). Advancements in Algorithms and Neuromorphic Hardware for Spiking Neural Networks. Neural Computation, 34(6), 1289-1328. https://doi.org/10.1162/neco\_a\_01499

DOI: 10.48175/IJARSCT-19435